# Hardware Architecture and Data Manipulation

## William W.-Y. Hsu

$\mathbf{2}$

Department of Computer Science and Engineering Department of Environmental Biology and Fisheries Science National Taiwan Ocean University

### CONTENTS

| 5  |

|----|

| 6  |

| 8  |

|    |

|    |

| 10 |

| 11 |

| 12 |

| 13 |

|    |

## 2.1 Introduction

The author of our textbook has designed a simple machine language for a theoretical computer, which uses the RISC instruction set architecture, discussed in Chapter 2 and Appendix C. This is called a simulator, which mimics the way a computer runs machine language programs. This simulator is very similar to modern computers as it has a *program counter* register, *instruction register*, 16 general purpose registers, and 256 bytes of main memory. It also contains an arithmetic & logic unit (ALU) which can perform ADD, AND, OR, XOR, and ROR operations. The memory of this virtual computer follows the von-neumann architecture, which can store both the machine program and data.

#### Introduction to Computers— Laboratory manual and exercises

The program that we will be using in this laboratory is a Windows program so you can execute it on any PC. Moreover, we also provide a C source code version that you can compile it for any other target platforms. Upon execution, you will see the GUI of the simulator as shown in Figure 2.1.

|     |    |      |    |              |    |    | Ма | iin N | /lem | ory |    |    |    |    |    |    |    | Re | qister   | 5             |   |

|-----|----|------|----|--------------|----|----|----|-------|------|-----|----|----|----|----|----|----|----|----|----------|---------------|---|

|     | 0  | 1    | 2  | 3            | 4  | 5  | 6  | 7     | 8    | 9   | A  | В  | C  | D  | E  | F  |    |    | _        |               |   |

| 00  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RO | 00 | PC (     | 00 =          | 0 |

| 10  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | B1 | 00 | IB (     | 0000          | Π |

| 20  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R2 | 00 |          |               |   |

| 30  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R3 | 00 | P        | <u>)</u> Open |   |

| 40  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R4 | 00 |          |               | - |

| 50  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R5 | 00 | G        | Save          |   |

| 60  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R6 | 00 |          |               | - |

| 70  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | B7 | 00 |          |               |   |

| 80  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R8 | 00 | N        | _             |   |

| 90  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | R9 | 00 |          | <u>R</u> un   |   |

| A0  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | BA | 00 | 225      |               |   |

| BO  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RB | 00 | Ē        | Step          |   |

| CO  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RC | 00 |          |               |   |

| DO  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RD | 00 |          | Break         |   |

| E0  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RE | 00 | <b>–</b> |               |   |

| FO  | 00 | 00   | 00 | 00           | 00 | 00 | 00 | 00    | 00   | 00  | 00 | 00 | 00 | 00 | 00 | 00 | RF | 00 |          | ) Clear       | _ |

| 00  |    | 0,00 |    | nval         | id |    |    |       |      |     |    |    |    |    |    | ^  |    |    |          |               | F |

| 02  |    | 0,00 |    | nval         |    |    |    |       |      |     |    |    |    |    |    |    |    |    |          |               |   |

| 04: |    | 0,00 |    | nval<br>nval |    |    |    |       |      |     |    |    |    |    |    |    |    |    |          |               |   |

| 08  |    | 0,00 |    | nval         |    |    |    |       |      |     |    |    |    |    |    |    | _  |    |          |               | 4 |

#### FIGURE 2.1

The virtual architecture simulator GUI.

## 2.2 Simulators

Programs, including assembly language, are for human to understand. A CPU can only execute the instruction code of a machine language, which is rather difficult for a human to write directly. This simulator provides a interface for loading assembly languages and convert it into machine language for the virtual CPU to run. The Open button in Figure 2.1 can load an assembly program, usually stored as a \*.asm file.

Hardware Architecture and Data Manipulation

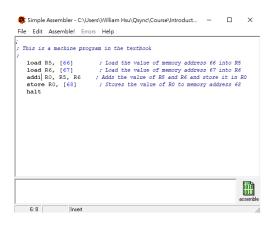

By using the **Open** button, we can load an assembly program. Suppose we load the **textbook.asm** file, with the contents as follows:

| 1 | ; | This is a | machine         | program in  | the te  | $\mathbf{xtbook}$ |          |       |         |         |

|---|---|-----------|-----------------|-------------|---------|-------------------|----------|-------|---------|---------|

|   |   | load R5,  | $[0 \times 6C]$ | ; Load the  | value   | of memory         | address  | 0x6C  | into H  | R5      |

| 3 |   | load R6,  | $[0 \times 6D]$ | ; Load the  | value   | of memory         | address  | 0x6D  | into H  | R6      |

|   |   | addi R0,  | R5, R6          | ; Adds the  | value   | of R5 and         | R6 and   | store | it in   | R0      |

| 5 |   | store R0, | $[0 \times 6E]$ | ; Stores th | ne valu | ie of R0 to       | o memory | addre | ess 0x6 | $_{6}E$ |

|   |   | halt      |                 |             |         |                   |          |       |         |         |

we get an editor showing the following assembly code in Figure 2.2.

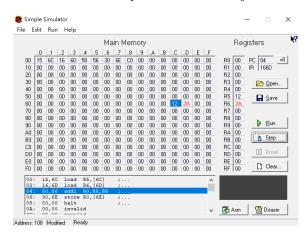

#### FIGURE 2.2

Loading an assembly file into the simulator.

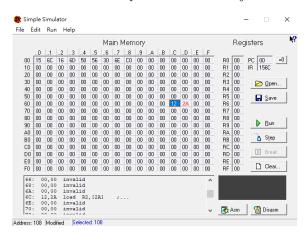

After the program has been loaded into the editor, we can push the **assemble** button to convert the assembly language into machine codes. Shown in Figure 2.3, the machine code has been stored at memory 0x00, and the *program counter* register (PC) is set to 00, which is the beginning of the program. You can verify to see if the assembly code converts to the machine code as listed in the PPT slides of the main course (or Figure 2.2 in the textbook). The machine instruction is stored starting at address 0x00, 156C166D5056306EC0.

Before we start to execute the program, we need to fill in values for address 0x6C and 0x6D. For example, we can put in the value 0x12 and 0x2A respectively. The simulator has a button Run

Introduction to Computers— Laboratory manual and exercises

### FIGURE 2.3

Converting the assembly file into machine code.

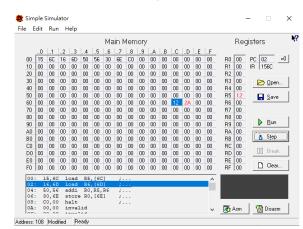

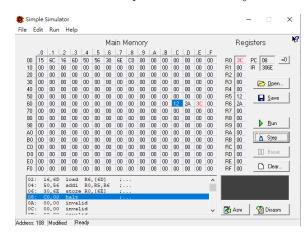

which executes the program from the beginning to the end, and a **Step** functionality to run the program line by line. We will use the **step** button to demonstrate. Starting from PC=0x00, after we press **step** once, we get the results shown in Figure 2.4. The current PC has been increased to PC=0x02, pointing to the next instruction to be fetched, and the *instruction register* IR=0x156C, meaning the instruction that has just been executed. We see that after executing 0x156C, the contents of register R5=0x12, which is copied from the memory address 0x6C.

The result of second step, executing the instruction IR=0x166D is shown in Figure 2.5. We can see that the value of register R6=0x2A is now copied from the memory address 0x6D.

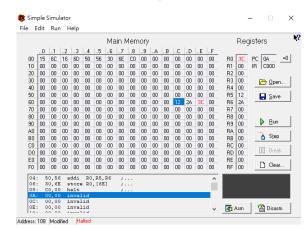

The third instruction 0x5056, conducts integer addition of the registers R5 and R6 and stores the result in R0=0x3C (see Figure 2.6).

The fourth instruction stores the content of register R0 back into memory address 0x6E (see Figure 2.7), and the last instruction 0xC000 end the program (see Figure 2.8).

Hardware Architecture and Data Manipulation

### 2.3 Complete instruction set

The complete instruction set for this virtual architecture is listed in Table.

### 2.4 Simple instruction combinations

The RISC instruction set can be combined to generate complex function. We will demonstrate some of them in this section.

#### 2.4.1 Immediate, direct, and indirect addressing

There are three modes of addressing that can be used in this simulator. Consider the following instructions:

load R1, 0x64 load R1, [0x64] load R1, [R5]

Introduction to Computers— Laboratory manual and exercises

**FIGURE 2.5** Executing 0x156D.

The first instruction is *immediate* instructions, which loads the value 0x64 into register R1. The second instruction is direct addressing, which loads the value stored in memory address 0x64 into register R1. The last instruction is indirect addressing, similar to pointer concept in C. It loads the value of the memory address stored in register R5 into register R1. These instructions are similar to the following C code:

$\begin{array}{c} a = 100; \\ a = b; \\ a = b; \\ a = *b; \\ // \ \mbox{where } b \ \mbox{has been assigned the value 100 before} \\ \end{array}$

#### 2.4.2 Branching

Consider the following C code:

```

\frac{if(a = 10)}{;} // Conditional branch test

\frac{if(a = 10)}{;} // then construct

\frac{else}{;} // else construct

```

This code can be implemented using the jmpEQ instruction.

|   | ; A branching structure |                                 |  |

|---|-------------------------|---------------------------------|--|

| 2 | load R0, 0x0A           | ; Loads the value 10 into R0    |  |

|   |                         | ; Let R1 be some value          |  |

| 4 | jmpEQ R1=R0, A          | ; Jumps to label A if $R1 = R0$ |  |

Hardware Architecture and Data Manipulation

|          |     |      |     |             |      |        | Ma        | ain N | /len | nory |    |    |    |    |    |          |          | Re | gister  | s            |

|----------|-----|------|-----|-------------|------|--------|-----------|-------|------|------|----|----|----|----|----|----------|----------|----|---------|--------------|

|          | 0   | 1    | 2   | 3           | 4    | 5      | 6         | 7     | 8    | 9    | A  | B  | C  | D  | E  | F        |          |    |         |              |

| 00       | 15  | 6C   | 16  | 6D          | 50   | 56     | 30        | 6E    | C0   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R0       | 30 | PC 1    | 06           |

| 10       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | B1       | 00 | IR !    | 5056         |

| 20       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R2       | 00 |         |              |

| 30       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R3       | 00 |         | Dpen.        |

| 40       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R4       | 00 |         |              |

| 50       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R5       | 12 | - E     | <u>S</u> ave |

| 60       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 12 | 2A | 00 | 00       | R6       | 2A |         |              |

| 70       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R7       | 00 |         |              |

| 80       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R8       | 00 |         | Run          |

| 90       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | R9       | 00 |         | nun          |

| A0       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | RA       | 00 | 1       | Step         |

| BO       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | RB       | 00 | <u></u> |              |

| C0       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | RC       | 00 | П       | Break        |

| D0<br>E0 | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | RD<br>BE | 00 |         | 1 broan      |

| FO       | 00  | 00   | 00  | 00          | 00   | 00     | 00        | 00    | 00   | 00   | 00 | 00 | 00 | 00 | 00 | 00       | BE       | 00 | C       | ) Clear      |

| 00       | . 1 | 5,60 | - 1 | oad         | 25   | , [60  | 1         | 1.    |      |      |    |    |    |    |    | ^        |          | ,  |         |              |

| 02       |     | 6,61 |     | oad         |      | , [ EE |           |       |      |      |    |    |    |    |    | <u> </u> |          |    |         |              |

| 04       |     | 0,50 |     | ddi         |      | ,R5,   |           |       |      |      |    |    |    |    |    |          |          |    |         |              |

| 06       |     | 0,61 |     | tore<br>alt | s RO | ,[GE   | <u>11</u> | 1.    |      |      |    |    |    |    |    |          |          |    |         |              |

**FIGURE 2.6** Executing 0x5056.

| 6  | jmp Exit      | ; | 'else' part of code<br>Unconditionally jump to label Exit |

|----|---------------|---|-----------------------------------------------------------|

| 8  | A:            | ; | 'then' part of code                                       |

| 10 | Exit:<br>halt | ; | Outside the if-then-else structure                        |

# 2.4.3 Looping

$\mathbf{2}$

Consider the following C code:

```

\frac{int}{for} a;

for(a = 0; a < 100; a++);

```

We can convert the above program into a assembly code using jmpLE instructions to mimic looping. Using R5 to represent the variable **a**, we use it as the control variable to detect wether we should continue looping or not. In additions, we have to convert constants within the C program and store it somewhere. Here we put the value 100 (or 0x64 in hexadecimal) in R0 for jmpLE to compare. Also, we need the value 1 for increment, so we store the value into R1.

```

1 ; A looping code

load R0, 0x64 ; Loads the value 100 into R0

```

Introduction to Computers— Laboratory manual and exercises

**FIGURE 2.7** Executing 0x306E.

#### 2.5 Lab Questions

- Write a program to compute the **XOR** value of address 0x6C, 0x6D, and store the results in address 0x6E.

- Write a program to swap the values of memory location of 0xA0 and 0xB0.

- Fill in the values 0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xA into the memory location starting from 0x50. Write a assembly program and add the values within the memory locations 0x50 to 0x59 and store it into memory location 0x40.

Hardware Architecture and Data Manipulation

**FIGURE 2.8** Executing 0xC000.

- Write a program to add the values of 1 to x, where 1 ≤ x ≤ 20.

(x can be stored in some register)

- For the program in Figure 2.2, instead of adding the value of memory address 0x6C and 0x6D, i.e., 0x6C + 0x6D, change the program with the available instructions to do subtraction, i.e., 0x6D - 0x6D.

- (Hard) Write a program to perform bubble sort within the memory locations of 0xC0 to 0xCF. (Requires using Op-code D and E)

#### 2.6 Lab Report

Your lab report is due before the next class.

Introduction to Computers— Laboratory manual and exercises

| Machine i | instruction |                      |                                                                                                                                                |

|-----------|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Op-code   | Operand     | Assembly Instruction | Operation                                                                                                                                      |

| 1         | RXY         | load R, [XY]         | Load R with the content from the<br>memory cell at address XY                                                                                  |

| 2         | RXY         | load R, XY           | Load R with the bit pattern XY                                                                                                                 |

| 3         | RXY         | store R, [XY]        | Store the content of R into the memory cell at address XY                                                                                      |

| 4         | 0RS         | move S, R            | Move content of R into S                                                                                                                       |

| 5         | RST         | addi R, S, T         | Add S and T and put the result<br>in R (R, S, and T are in two's<br>complement integer notation)                                               |

| 6         | RST         | addf R, S, T         | Add S and T and put the result<br>in R (R, S, and T are in floating-<br>point notation)                                                        |

| 7         | RST         | or R, S, T           | OR the bit patterns in S and T<br>and put the result in R                                                                                      |

| 8         | RST         | and R, S, T          | AND the bit patterns in S and T<br>and put the result in R                                                                                     |

| 9         | RST         | xor R, S, T          | XOR the bit patterns in S and T<br>and put the result in R                                                                                     |

| А         | R0X         | ror R, X             | Circularly rotate the bit pattern<br>in R one bit to the right X times                                                                         |

| В         | RXY         | jmpEQ R=R0, XY       | Start decoding the instruction lo-<br>cated at address XY if the bit<br>pattern in R is equal to the bit<br>pattern in register 0              |

| С         | 000         | halt                 | Halt execution                                                                                                                                 |

| D         | ORS         | load R, [S]          | Load R with the content from the<br>memory cell whose address is in<br>S                                                                       |

| Ε         | ORS         | store R, [S]         | Store the content of R into the memory cell whose address is in S                                                                              |

| F         | RXY         | jmpLE R<=R0, XY      | Start decoding the instruction lo-<br>cated at address XY if the bit<br>pattern in R is less than or equal<br>to the bit pattern in register 0 |

|           |             | jmp XY               | Unconditional jump to address XY                                                                                                               |

|           |             | db XY                | Creates a static space at address<br>XY filled with data                                                                                       |

# TABLE 2.1

The instruction set of the simulator.